技術中心

減少無法加工的風險,解密生產(chǎn)制造,了解行業(yè)規(guī)范和術語,提升行業(yè)技能

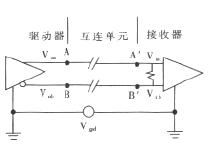

差分信號線的分析和LAYOUT隨著近幾年對速率的要求快速提高,新的總線協(xié)議不斷的提出更高的速率。傳統(tǒng)的總線協(xié)議已經(jīng)不能夠滿足要求了。串行總線由于更好的抗干擾性,和更少的信號線,更高的速率獲得了眾多設計者的青睞。而串行總線又尤以差分信號的方式為最多。所以在這篇中整理了些有關差分信號線的設計和大家探討下...

差分信號線的分析和LAYOUT隨著近幾年對速率的要求快速提高,新的總線協(xié)議不斷的提出更高的速率。傳統(tǒng)的總線協(xié)議已經(jīng)不能夠滿足要求了。串行總線由于更好的抗干擾性,和更少的信號線,更高的速率獲得了眾多設計者的青睞。而串行總線又尤以差分信號的方式為最多。所以在這篇中整理了些有關差分信號線的設計和大家探討下... 2014-09-18

2014-09-18 10279

10279 淺談PCB的阻抗控制隨著電路設計日趨復雜和高速,如何保證各種信號(特別是高速信號)完整性,也就是保證信號質(zhì)量,成為難題。此時,需要借助傳輸線理論進行分析,控制信號線的特征阻抗匹配成為關鍵,不嚴格的阻抗控制,將引發(fā)相當大的信號反射和信號失真,導致設計失敗。常見的信號,如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)存、LVDS信號等,均需要進行阻抗控制....

淺談PCB的阻抗控制隨著電路設計日趨復雜和高速,如何保證各種信號(特別是高速信號)完整性,也就是保證信號質(zhì)量,成為難題。此時,需要借助傳輸線理論進行分析,控制信號線的特征阻抗匹配成為關鍵,不嚴格的阻抗控制,將引發(fā)相當大的信號反射和信號失真,導致設計失敗。常見的信號,如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)存、LVDS信號等,均需要進行阻抗控制.... 2014-09-18

2014-09-18 8067

8067 高速PCB可控性與電磁兼容性設計隨著系統(tǒng)設計復雜性和集成度的大規(guī)模提高,電子系統(tǒng)設計師們正在從事100MHZ以上的電路設計,總線的工作頻率也已經(jīng)達到或者超過50MHZ,有的甚至超過100MHZ。目前約50% 的設計的時鐘頻率超過50MHz,將近20% 的設計主頻超過120MHz...

高速PCB可控性與電磁兼容性設計隨著系統(tǒng)設計復雜性和集成度的大規(guī)模提高,電子系統(tǒng)設計師們正在從事100MHZ以上的電路設計,總線的工作頻率也已經(jīng)達到或者超過50MHZ,有的甚至超過100MHZ。目前約50% 的設計的時鐘頻率超過50MHz,將近20% 的設計主頻超過120MHz... 2014-09-18

2014-09-18 6176

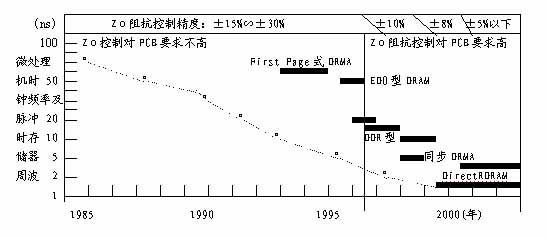

6176 PCB特性阻抗控制精度探討 隨著以計算機為先導的電路信號傳輸高速化的迅速發(fā)展,其中一個非常重要的問題就是:要求PCB在高速信號傳輸中保持信號穩(wěn)定,不產(chǎn)生誤動作,這就要求所使用的PCB的特性阻抗控制精度化的提高。

PCB特性阻抗控制精度探討 隨著以計算機為先導的電路信號傳輸高速化的迅速發(fā)展,其中一個非常重要的問題就是:要求PCB在高速信號傳輸中保持信號穩(wěn)定,不產(chǎn)生誤動作,這就要求所使用的PCB的特性阻抗控制精度化的提高。 2014-09-18

2014-09-18 9221

9221 經(jīng)典總結(jié):不得不知的PCB設計技巧(2)PCB設計中經(jīng)典技巧總結(jié),各種PCB設計中的問題解讀,讓你的PCB設計少走彎路...

經(jīng)典總結(jié):不得不知的PCB設計技巧(2)PCB設計中經(jīng)典技巧總結(jié),各種PCB設計中的問題解讀,讓你的PCB設計少走彎路... 2014-09-17

2014-09-17 9713

9713