技術(shù)中心

減少無法加工的風(fēng)險(xiǎn),解密生產(chǎn)制造,了解行業(yè)規(guī)范和術(shù)語,提升行業(yè)技能

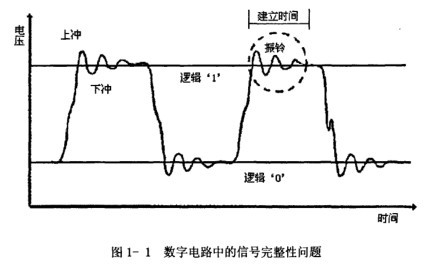

PCB設(shè)計(jì)進(jìn)階:PCB設(shè)計(jì)信號(hào)完整性的修煉如果你發(fā)現(xiàn),以前低速時(shí)代積累的設(shè)計(jì)經(jīng)驗(yàn)現(xiàn)在似乎都不靈了,同樣的設(shè)計(jì),以前沒問題,可是現(xiàn)在卻無法工作,那么恭喜你,你碰到了硬件設(shè)計(jì)中最核心的問題:信號(hào)完整性...

PCB設(shè)計(jì)進(jìn)階:PCB設(shè)計(jì)信號(hào)完整性的修煉如果你發(fā)現(xiàn),以前低速時(shí)代積累的設(shè)計(jì)經(jīng)驗(yàn)現(xiàn)在似乎都不靈了,同樣的設(shè)計(jì),以前沒問題,可是現(xiàn)在卻無法工作,那么恭喜你,你碰到了硬件設(shè)計(jì)中最核心的問題:信號(hào)完整性... 2014-09-29

2014-09-29 8742

8742 利用 Cadence Allegro PCB 高速電路有兩個(gè)方面的含義, 一是頻率高, 通常認(rèn)為數(shù)字電路的頻率達(dá)到或是超45MHZ至50MHZ,而且工作在這個(gè)頻率之上的電路已經(jīng)占到了整個(gè)系統(tǒng)的三分之一,就稱為高速電路;二是從信號(hào)的上升與下降時(shí)間考慮,當(dāng)信號(hào)的上升時(shí)小于6倍信號(hào)傳輸延時(shí)時(shí)即認(rèn)為信號(hào)是高速信號(hào)

利用 Cadence Allegro PCB 高速電路有兩個(gè)方面的含義, 一是頻率高, 通常認(rèn)為數(shù)字電路的頻率達(dá)到或是超45MHZ至50MHZ,而且工作在這個(gè)頻率之上的電路已經(jīng)占到了整個(gè)系統(tǒng)的三分之一,就稱為高速電路;二是從信號(hào)的上升與下降時(shí)間考慮,當(dāng)信號(hào)的上升時(shí)小于6倍信號(hào)傳輸延時(shí)時(shí)即認(rèn)為信號(hào)是高速信號(hào) 2014-09-26

2014-09-26 13427

13427 PCB信號(hào)完整性分析與設(shè)計(jì)(碩士學(xué)位論文)串?dāng)_是信號(hào)線間的耦合,是由信號(hào)線之間的互感和互容引起的噪聲。串?dāng)_耦合通常可分為兩種,即公共阻抗耦合和電磁場(chǎng)耦合。公共阻抗耦合是因?yàn)椴煌盘?hào)共用公共返回路徑引起的,這種耦合通常在低頻時(shí)起決定作用...

PCB信號(hào)完整性分析與設(shè)計(jì)(碩士學(xué)位論文)串?dāng)_是信號(hào)線間的耦合,是由信號(hào)線之間的互感和互容引起的噪聲。串?dāng)_耦合通常可分為兩種,即公共阻抗耦合和電磁場(chǎng)耦合。公共阻抗耦合是因?yàn)椴煌盘?hào)共用公共返回路徑引起的,這種耦合通常在低頻時(shí)起決定作用... 2014-09-26

2014-09-26 10050

10050 EMI/EMC設(shè)計(jì)秘籍——電子產(chǎn)品設(shè)計(jì)工程師必一、EMC 工程師必須具備的八大技能;二、EMC 常用元件三;、EMI/EMC 設(shè)計(jì)經(jīng)典85問;四、EMC 專用名詞大全;五、產(chǎn)品內(nèi)部的 EMC 設(shè)計(jì)技巧;六、電磁干擾的屏蔽方法;七、電磁兼容(EMC)設(shè)計(jì)如何融入產(chǎn)品研發(fā)流程...

EMI/EMC設(shè)計(jì)秘籍——電子產(chǎn)品設(shè)計(jì)工程師必一、EMC 工程師必須具備的八大技能;二、EMC 常用元件三;、EMI/EMC 設(shè)計(jì)經(jīng)典85問;四、EMC 專用名詞大全;五、產(chǎn)品內(nèi)部的 EMC 設(shè)計(jì)技巧;六、電磁干擾的屏蔽方法;七、電磁兼容(EMC)設(shè)計(jì)如何融入產(chǎn)品研發(fā)流程... 2014-09-26

2014-09-26 7769

7769 高速電路設(shè)計(jì)之阻抗控制與阻抗計(jì)算組件自身可以顯示特性阻抗,因此必須選擇PC B跡線阻抗來匹配使用中的所有邏輯系列的特性阻抗(對(duì)于 CMOS 和TTL,特性阻抗的范圍是 50 到 110 歐姆)。為了最好地將信號(hào)從源傳送到負(fù)載,跡線阻抗必須匹配發(fā)送設(shè)備的輸出阻抗和接收設(shè)備的輸入阻抗...

高速電路設(shè)計(jì)之阻抗控制與阻抗計(jì)算組件自身可以顯示特性阻抗,因此必須選擇PC B跡線阻抗來匹配使用中的所有邏輯系列的特性阻抗(對(duì)于 CMOS 和TTL,特性阻抗的范圍是 50 到 110 歐姆)。為了最好地將信號(hào)從源傳送到負(fù)載,跡線阻抗必須匹配發(fā)送設(shè)備的輸出阻抗和接收設(shè)備的輸入阻抗... 2014-09-26

2014-09-26 7866

7866